Veja as especificações para detalhes do produto.

EP20K1000EFC33-1

Product Overview

Category

The EP20K1000EFC33-1 belongs to the category of programmable logic devices (PLDs).

Use

This product is primarily used in digital circuit design and implementation. It provides a flexible and customizable solution for various applications.

Characteristics

- Programmable: The EP20K1000EFC33-1 can be programmed to perform specific functions based on user requirements.

- High-density: It offers a high number of logic elements, allowing for complex designs.

- Versatile: This PLD supports a wide range of applications due to its programmability.

- Low power consumption: The EP20K1000EFC33-1 is designed to operate efficiently with minimal power consumption.

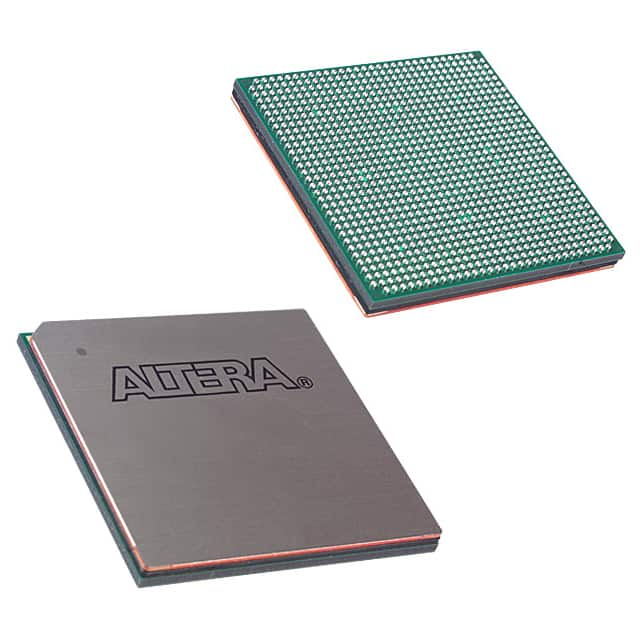

Package

The EP20K1000EFC33-1 comes in a compact package that ensures easy integration into electronic circuits. It is available in a surface-mount package.

Essence

The essence of this product lies in its ability to provide a reconfigurable hardware platform for implementing digital logic functions.

Packaging/Quantity

The EP20K1000EFC33-1 is typically packaged in reels or trays, depending on the manufacturer's specifications. The quantity per package may vary, but it is commonly available in quantities of 100 or more.

Specifications

- Device Type: Programmable Logic Device (PLD)

- Family: EP20K

- Model: 1000EFC33-1

- Operating Temperature: -40°C to +85°C

- Supply Voltage: 3.3V

- Logic Elements: 1000

- I/O Pins: 33

- Speed Grade: 1

Detailed Pin Configuration

The EP20K1000EFC33-1 has a total of 33 I/O pins. These pins are used for input and output connections to external devices. The pin configuration is as follows:

- Pin 1: VCCIO

- Pin 2: GND

- Pin 3: IO0

- Pin 4: IO1

- Pin 5: IO2

- Pin 6: IO3

- Pin 7: IO4

- Pin 8: IO5

- Pin 9: IO6

- Pin 10: IO7

- Pin 11: IO8

- Pin 12: IO9

- Pin 13: IO10

- Pin 14: IO11

- Pin 15: IO12

- Pin 16: IO13

- Pin 17: IO14

- Pin 18: IO15

- Pin 19: IO16

- Pin 20: IO17

- Pin 21: IO18

- Pin 22: IO19

- Pin 23: IO20

- Pin 24: IO21

- Pin 25: IO22

- Pin 26: IO23

- Pin 27: IO24

- Pin 28: IO25

- Pin 29: IO26

- Pin 30: IO27

- Pin 31: IO28

- Pin 32: IO29

- Pin 33: IO30

Functional Features

- Reconfigurability: The EP20K1000EFC33-1 can be reprogrammed multiple times, allowing for design modifications and updates.

- High-speed operation: This PLD offers fast processing capabilities, enabling efficient execution of digital logic functions.

- I/O Flexibility: With 33 I/O pins, the EP20K1000EFC33-1 provides flexibility in connecting to external devices and peripherals.

- Embedded Memory: It includes embedded memory blocks that can be used for data storage or as lookup tables.

Advantages and Disadvantages

Advantages

- Flexibility: The EP20K1000EFC33-1 allows for customization and adaptation to specific design requirements.

- Cost-effective: By eliminating the need for custom hardware, this PLD reduces development costs.

- Time-saving: With its reprogrammable nature, it enables faster prototyping and design iterations.

Disadvantages

- Learning curve: Utilizing programmable logic devices requires knowledge of hardware description languages and digital design concepts.

- Limited performance: While suitable for many applications, PLDs may not offer the same level of performance as dedicated ASICs (Application-Specific Integrated Circuits).

Working Principles

The EP20K1000EFC33-1 operates based on the principles of field-programmable gate arrays (FPGAs). It consists of a matrix of configurable logic blocks (CLBs) interconnected through programmable interconnects. These CL

Liste 10 perguntas e respostas comuns relacionadas à aplicação de EP20K1000EFC33-1 em soluções técnicas

Sure! Here are 10 common questions and answers related to the application of EP20K1000EFC33-1 in technical solutions:

Q1: What is EP20K1000EFC33-1? A1: EP20K1000EFC33-1 is a specific model of Field Programmable Gate Array (FPGA) manufactured by Intel (formerly Altera). It is designed for high-performance applications and offers a range of features and capabilities.

Q2: What are the key features of EP20K1000EFC33-1? A2: Some key features of EP20K1000EFC33-1 include a large number of logic elements, embedded memory blocks, high-speed I/O interfaces, programmable interconnects, and support for various communication protocols.

Q3: What are the typical applications of EP20K1000EFC33-1? A3: EP20K1000EFC33-1 is commonly used in applications such as telecommunications, networking equipment, industrial automation, video processing, medical devices, and aerospace systems.

Q4: How can EP20K1000EFC33-1 be programmed? A4: EP20K1000EFC33-1 can be programmed using Hardware Description Languages (HDLs) like VHDL or Verilog. Designers write code in these languages and use specialized software tools provided by Intel to compile and configure the FPGA.

Q5: Can EP20K1000EFC33-1 be reprogrammed? A5: Yes, EP20K1000EFC33-1 is a reprogrammable FPGA. It can be reconfigured multiple times, allowing for flexibility in design iterations and updates.

Q6: What is the maximum operating frequency of EP20K1000EFC33-1? A6: The maximum operating frequency of EP20K1000EFC33-1 depends on the specific design and implementation. However, it is capable of operating at high frequencies, typically in the range of hundreds of megahertz to a few gigahertz.

Q7: Does EP20K1000EFC33-1 support external memory interfaces? A7: Yes, EP20K1000EFC33-1 supports various external memory interfaces such as DDR, SDRAM, SRAM, and Flash memory. These interfaces can be used to store and retrieve data during FPGA operation.

Q8: Can EP20K1000EFC33-1 interface with other electronic components or devices? A8: Yes, EP20K1000EFC33-1 provides a range of I/O interfaces including LVDS, differential signaling, single-ended signaling, and serial communication protocols like SPI and I2C. This allows for seamless integration with other electronic components and devices.

Q9: What are the power requirements for EP20K1000EFC33-1? A9: EP20K1000EFC33-1 requires a supply voltage of 3.3V for core logic and I/O operations. Additionally, it may require additional power supplies for specific features or peripherals depending on the design requirements.

Q10: Are there any development boards or evaluation kits available for EP20K1000EFC33-1? A10: Yes, Intel provides development boards and evaluation kits specifically designed for EP20K1000EFC33-1. These kits include all the necessary hardware and software tools to facilitate the development and testing of FPGA designs using this specific model.

Please note that the answers provided here are general and may vary based on specific design requirements and application scenarios.